# 4-Bit, Single-Chip CMOS Microcomputers With LCD Controller/Driver

T-49-19-40

#### **Description**

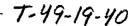

The  $\mu$ PD7502 and  $\mu$ PD7503 4-bit, single-chip CMOS microcomputers have advanced fourth-generation architecture with the functional blocks necessary for a single-chip controller, including an 8-bit timer/event counter, an 8-bit serial I/O, and an LCD controller/driver.

The instruction set includes the following types of instructions: addressing, table look-up, bit manipulation, vectored jump, auto increment or decrement data pointer, and conditional skip. These instructions maximize use of fixed program memory space.

Both devices are manufactured with the CMOS process and have a maximum power consumption of 900  $\mu$ A at 5 V and 300  $\mu$ A at 3 V. Halt and stop modes further reduce power consumption.

These devices are ideal for a wide range of solar- and battery-powered applications.

#### **Features**

- ☐ 92 powerful instructions

- □ Program ROM

- μPD7502; 2048 x 8-bit

- μPD7503: 4096 x 8-bit

- ☐ Data RAM

- --- μPD7502: 128 x 4-bit

- -- μPD5703: 224 x 4-bit

- □ Interrupts

- External: INT0, INT1

- Internal: INTT (timer/event counter)

INTS (serial interface)

- □ 8-bit timer/event counter

- Based on crystal oscillation

- External event counter (prescale option by 64)

- ☐ Serial interface

- ☐ LCD controller/driver

- Programmable multiplexing mode: triplex, quadruplex, or pseudo-static

- 4 common lines (COM<sub>0</sub>-COM<sub>3</sub>)

- 24 segment lines (S<sub>0</sub>-S<sub>23</sub>)

- ☐ Standby modes: stop, half

- ☐ Data retention mode

- □ I/O ports

- 3-bit input port

- 4-bit input port

- 4-bit output port

- Two 4-bit I/O ports with 8-bit capability

- 4-bit I/O port with each bit configurable as an input or output

☐ RC oscillation clock

- ☐ Crystal oscillation clock

- ☐ 2.5 to 6.0 V operating voltage

- □ CMOS technology

#### **Ordering Information**

| Part No.     | Part No. Package Type |         |

|--------------|-----------------------|---------|

| μPD7502GF-12 | 64-pin plastic QFP    | 410 kHz |

| μPD7503GF-12 | 64-pin plastic QFP    | 410 kHz |

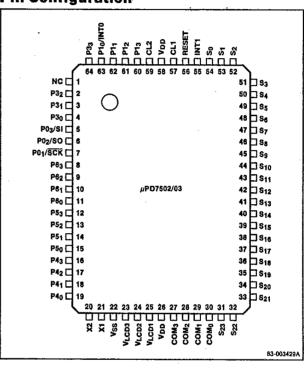

#### **Pin Configuration**

- T-49-19-40

#### Pin Identification

| No.     | Symbol                                                             | Function                                       |

|---------|--------------------------------------------------------------------|------------------------------------------------|

| 1       | NC                                                                 | No connection                                  |

| 2-4, 64 | P3 <sub>3</sub> -P3 <sub>0</sub>                                   | 4-bit output port 3                            |

| 5-7     | P0 <sub>3</sub> /SI<br>P0 <sub>2</sub> /S0<br>P0 <sub>1</sub> /SCK | 3-bit input port 0, or serial I/O interface    |

| 8-11    | P6 <sub>3</sub> -P6 <sub>0</sub>                                   | 4-bit I/O port 6                               |

| 12-15   | P53-P50                                                            | 4-bit I/O port 5                               |

| 16-19   | P43-P40                                                            | 4-bit 1/0 port 4                               |

| 20, 21  | X2, X1                                                             | Crystal clock/external event input port X      |

| 22      | Vss                                                                | Ground                                         |

| 23-25   | V <sub>LCD3</sub> -V <sub>LCD1</sub>                               | LCD blas supply inputs                         |

| 26, 58  | V <sub>DD</sub>                                                    | Positive power supply                          |

| 27-30   | COM <sub>3</sub> -COM <sub>0</sub>                                 | LCD backplane driver outputs                   |

| 31-54   | S <sub>23</sub> -S <sub>0</sub>                                    | LCD segment driver outputs                     |

| 55      | INT1                                                               | External interrupt                             |

| 56      | RESET                                                              | RESET input                                    |

| 57, 59  | CL1, CL2                                                           | System clock input                             |

| 60-63   | P1 <sub>3</sub> -P1 <sub>1</sub> ,<br>P1 <sub>0</sub> /INT0        | 4-bit input port 1, or external interrupt INTO |

### Status of Unused Pins

| Name                                                                                                          | Pin Connection                                                      |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| CL2                                                                                                           | Open                                                                |

| X1                                                                                                            | V <sub>SS</sub>                                                     |

| X2                                                                                                            | Open .                                                              |

| P0 <sub>1</sub> /SCK<br>P0 <sub>2</sub> /S0<br>P0 <sub>3</sub> /SI                                            | V <sub>SS</sub> or V <sub>DD</sub>                                  |

| P1 <sub>0</sub> /INT0                                                                                         | V <sub>SS</sub>                                                     |

| P1 <sub>1</sub> -P1 <sub>3</sub>                                                                              | V <sub>SS</sub> or V <sub>DD</sub>                                  |

| P3 <sub>0</sub> -P3 <sub>3</sub>                                                                              | Open                                                                |

| P4 <sub>0</sub> -P4 <sub>3</sub><br>P5 <sub>0</sub> -P5 <sub>3</sub><br>P6 <sub>0</sub> -P6 <sub>3</sub>      | Input mode: V <sub>SS</sub> or V <sub>DD</sub><br>Output mode: Open |

| INT1                                                                                                          | V <sub>SS</sub>                                                     |

| S <sub>0</sub> -S <sub>23</sub><br>COM <sub>0</sub> -COM <sub>3</sub><br>V <sub>LCD1</sub> -V <sub>LCD3</sub> | Open                                                                |

#### **Pin Functions**

## P0<sub>3</sub>/SI, P0<sub>2</sub>/SO, P0<sub>1</sub>/SCK [Port 0 or Serial Interface]

This port can be configured as a 4-bit parallel input port 0 or as the 8-bit serial I/O interface under control of the serial mode select register. The serial interface consists of the serial input (SI), the serial output (SO), and the serial clock (SCK), which synchronizes data transfer.

#### P1<sub>3</sub>-P1<sub>1</sub>, P1<sub>0</sub>/INT0 [Port 1 or Interrupt]

4-bit input port 1. Line P1<sub>0</sub> is shared with external interrupt INT0, which is a rising edge-triggered interrupt.

#### P3<sub>3</sub>-P3<sub>0</sub> [Port 3]

4-bit, latched three-state output port 3.

#### P43-P40 [Port 4]

4-bit input or latched three-state output port 4. Can perform 8-bit I/O in conjunction with port 5.

#### P53-P50 [Port 5]

4-bit input or latched three-state output port 5. Can perform 8-bit I/O in conjunction with port 4.

#### P63-P60 [Port 6]

4-bit input or latched three-state output port 6. The port 6 mode select register configures individual lines as inputs or outputs.

#### COM<sub>3</sub>-COM<sub>0</sub> [LCD Backplane Driver Outputs]

LCD backplane driver outputs.

#### \$23-S0 [LCD Segment Driver Outputs]

LCD segment driver outputs.

#### INT1 [Interrupt]

This external interrupt is a rising edge-triggered interrupt latched by CL.

#### RESET

A high-level input to this pin initializes the  $\mu$ PD7502/7503.

#### X2, X1 [Crystal Clock/External Event Input Port X]

For crystal clock operation, connect a crystal oscillator circuit to input X1 and output X2. For external event counting, input external event pulses to X1 and leave X2 open.

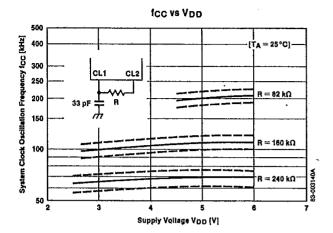

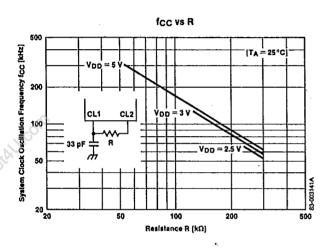

#### CL1, CL2 [System Clock Input]

Connect an 82-k $\Omega$  resistor across CL1 and CL2, and a 33-pF capacitor from CL1 to V<sub>SS</sub>. Or, connect an external clock source to CL1 and leave CL2 open.

#### V<sub>LCD3</sub>-V<sub>LCD1</sub> [LCD Bias Voltage Inputs]

LCD bias voltage supply inputs to the LCD voltage controller. Apply appropriate voltages from a voltage ladder connected across V<sub>DD</sub>.

#### $V_{DD}$

Positive power supply. For proper operation, apply a single voltage from 2.5 to 6.0 V.

#### Vss

Ground.

#### **Block Diagram**

See figures 1 through 8 for additional block diagram details.

| Figure | Title                           |

|--------|---------------------------------|

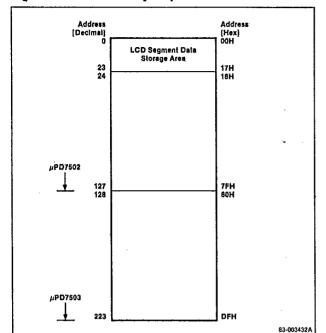

| 1      | Data Memory Map                 |

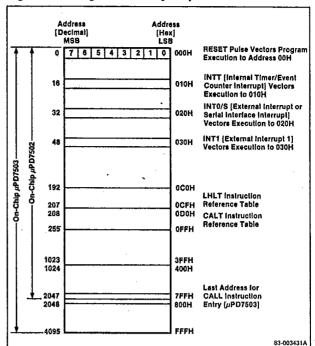

| 2      | Program Memory Map              |

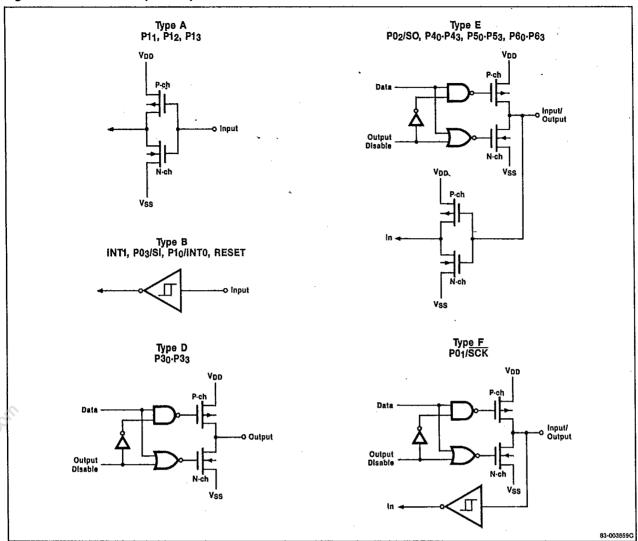

| 3      | Interface at Input/Output Ports |

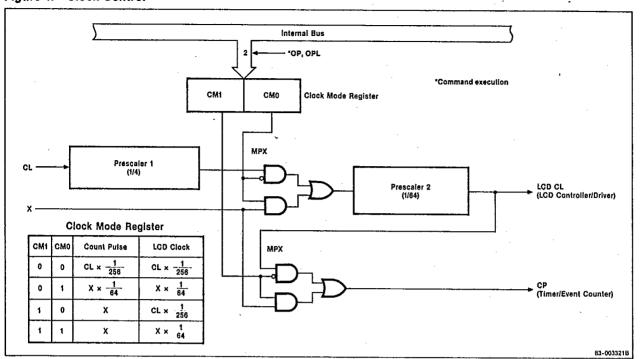

| 4      | Clock Control                   |

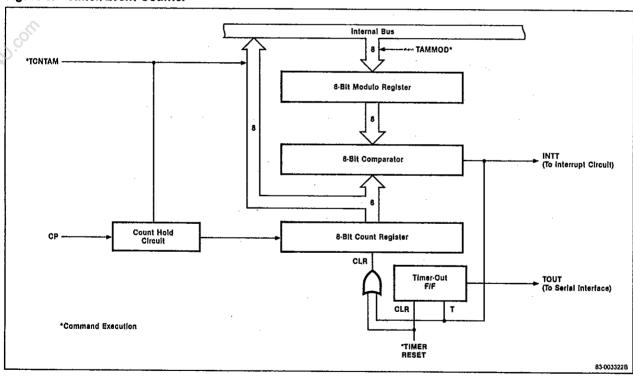

| 5      | Timer/Event Counter             |

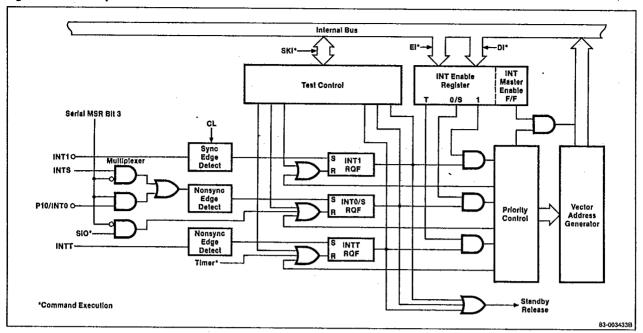

| 6      | Interrupt Control               |

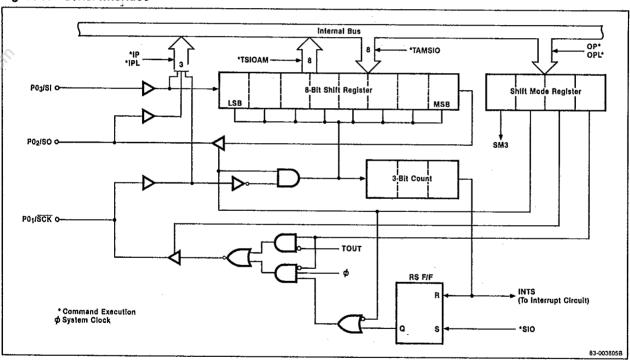

| 7      | Serial Interface                |

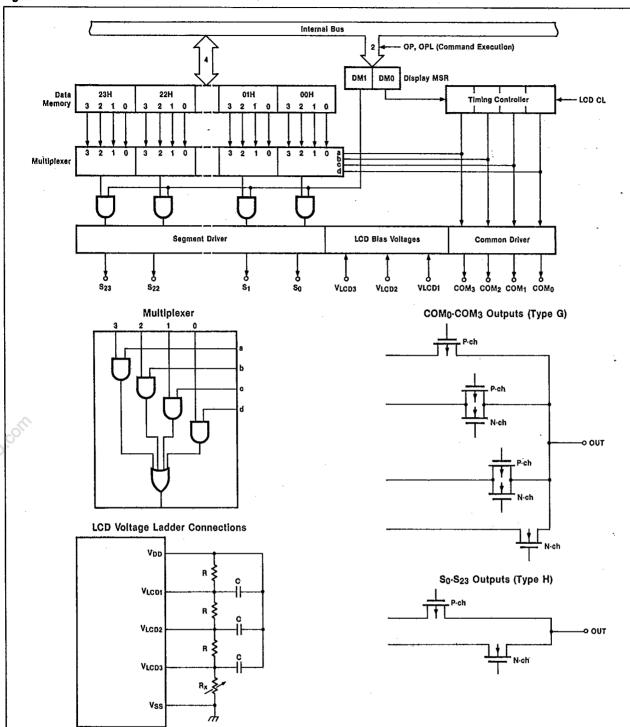

| 8      | LCD Controller/Driver           |

Figure 1. Data Memory Map

Figure 2. Program Memory Map

NES

Figure 3. Interface at Input/Output Ports

Figure 4. Clock Control

Figure 5. Timer/Event Counter

Figure 6. Interrupt Control

Figure 7. Serial Interface

NEC

T-49-19-40

Figure 8. LCD Controller/Driver

83-003325C

NEC

T-49-19-40

#### **Absolute Maximum Ratings**

$T_A = 25$ °C

| Power supply voltage, V <sub>DD</sub>                                  | -0.3 to +7.0 V                    |

|------------------------------------------------------------------------|-----------------------------------|

| All input and output voltages                                          | -0.3 V to V <sub>DD</sub> + 0.3 V |

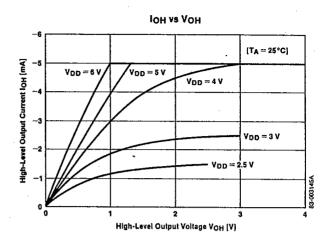

| Output current high, l <sub>OH</sub><br>Per pin<br>Total, output ports | —17 mA<br>—20 mA                  |

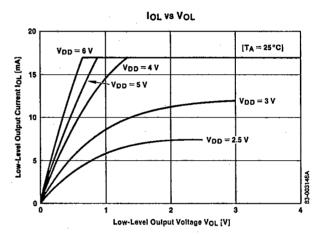

| Output current low, I <sub>OL</sub><br>Per pin<br>Total, output ports  | 17 mA<br>55 mA                    |

| Operating temperature, T <sub>OPT</sub>                                | −10 to +70°C                      |

| Storage temperature, T <sub>STG</sub>                                  | −65 to +150°C                     |

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification, Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Capacitance

$T_A = 25 \,^{\circ}C; V_{DD} = 0 \,^{\circ}V$

|                       |                 |     | Limits |     |     | Test                                 |

|-----------------------|-----------------|-----|--------|-----|-----|--------------------------------------|

| Parameter             | Symbol          | Min | Тур    | Max |     | Conditions                           |

| Input<br>capacitance  | Cį              |     |        | 15  | pF. | f <sub>C</sub> = 1 MHz<br>Unmeasured |

| Output<br>capacitance | C <sub>0</sub>  |     |        | 15  | pF  | pins returned to<br>V <sub>SS</sub>  |

| I/O<br>capacitance    | C <sub>IO</sub> |     |        | 15  | pF  |                                      |

#### **DC** Characteristics 1

For  $V_{DD} = 2.5$  to 3.3 Volts  $T_A = -10$  to +70 °C

|                              |                   |                       | Limits      |                     | <b>T</b> |                                                                                       |

|------------------------------|-------------------|-----------------------|-------------|---------------------|----------|---------------------------------------------------------------------------------------|

| Parameter                    | Symbol            | Min                   | Тур         | Max                 | Unit     | Test<br>Conditions                                                                    |

| input voltage, high          | V <sub>IH1</sub>  | 0.8 V <sub>DD</sub>   | <del></del> | V <sub>DD</sub>     | ٧        | Except CL1, X1                                                                        |

|                              | V <sub>IH2</sub>  | $V_{DD}-0.3$          |             | V <sub>DD</sub>     | ٧        | CL1, X1                                                                               |

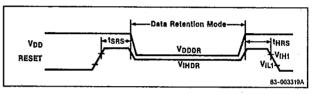

|                              | V <sub>IHDR</sub> | 0.9 V <sub>DDDR</sub> |             | $V_{DDDR} + 0.2$    | ٧        | RESET, data retention mode                                                            |

| nput voltage, low            | V <sub>IL1</sub>  | 0                     |             | 0.2 V <sub>DD</sub> | ٧        | Except CL1, X1                                                                        |

|                              | V <sub>IL2</sub>  | 0                     |             | 0.3                 | ٧        | CL1, X1                                                                               |

| Output voltage, high         | V <sub>OH</sub>   | $V_{DD} - 0.5$        |             |                     | ٧        | $I_{OH} = -80 \mu\text{A}$                                                            |

| Output voltage, low          | V <sub>OL</sub>   |                       |             | 0.5                 | V        | $I_{0L} = 350  \mu A$                                                                 |

| nput leakage current, high   | lLIH1             |                       |             | 3                   | μA       | Except CL1, X1; V <sub>IN</sub> = V <sub>DD</sub>                                     |

|                              | ILIH2             |                       |             | 10                  | μΑ       | CL1, X1; V <sub>IN</sub> = V <sub>DD</sub>                                            |

| nput leakage current, low    | I <sub>LIL1</sub> |                       |             | -3                  | μA       | Except CL1, X1; V <sub>IN</sub> = 0 V                                                 |

|                              | I <sub>LIL2</sub> |                       |             | 10                  | μA       | CL1, X1; V <sub>IN</sub> = 0 V                                                        |

| Output leakage current, high | ILOH              | -                     |             | 3                   | μΑ       | $V_0 = V_{DD}$                                                                        |

| lutput leakage current, low  | ILOL              |                       |             | -3                  | μA       | V <sub>0</sub> = 0 V                                                                  |

| Supply voltage               | V <sub>DDDR</sub> | 2.0                   |             |                     | ٧        | Data retention mode                                                                   |

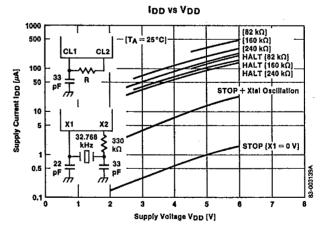

| Supply current               | l <sub>DD1</sub>  |                       | 50          | 250                 | μA       | Normal operation, $V_{DD}=3~V\pm10\%$ ; R = 240 k $\Omega\pm2\%$ , C = 33 pF $\pm5\%$ |

|                              |                   |                       | 35          | 230                 | μΑ       | Normal operation, $V_{DD}$ = 2.5 V;<br>R = 240 k $\Omega$ ±2%, C = 33 pF ±5%          |

|                              | I <sub>DD2</sub>  |                       | 0.3         | 10                  | μΑ       | Stop mode, X1 = 0 V; $V_{DD} = 3 \text{ V} \pm 10^{\circ}$                            |

|                              |                   |                       | 0.2         | 10                  | μΑ       | Stop mode, $X1 = 0 \text{ V}$ ; $V_{DD} = 2.5 \text{ V}$                              |

|                              | loddr             |                       | 0.2         | 10                  | μΑ       | Data retention mode, V <sub>DDDR</sub> = 2.0 V                                        |

#### **DC** Characteristics 2

For V<sub>DD</sub> = 2.7 to 6.0 Volts T<sub>A</sub> = -10 to +70 °C

|                              |                   |                       | Limits | -                       |      | Test                                                                                     |

|------------------------------|-------------------|-----------------------|--------|-------------------------|------|------------------------------------------------------------------------------------------|

| Parameter                    | Symbol            | Min                   | Тур    | Max                     | Unit | Conditions                                                                               |

| Input voltage, high          | V <sub>IH1</sub>  | 0.7 V <sub>DD</sub>   |        | V <sub>DD</sub>         | ٧    | Except CL1, X1                                                                           |

|                              | V <sub>IH2</sub>  | V <sub>DD</sub> 0.5   |        | V <sub>DD</sub>         | ٧    | CL1, X1                                                                                  |

| ·                            | V <sub>IHDR</sub> | 0.9 V <sub>DDDR</sub> |        | V <sub>DDDR</sub> + 0.2 |      | RESET, data retention mode                                                               |

| Input voltage, low           | V <sub>IL1</sub>  | 0                     | -      | 0.3 V <sub>DD</sub>     | V    | Except CL1, X1                                                                           |

|                              | V <sub>IL2</sub>  | 0                     |        | 0.5                     | ٧    | CL1, X1                                                                                  |

| Output voltage, high         | V <sub>OH</sub>   | $V_{DD} - 1.0$        |        |                         | ٧    | $I_{OH} = -1.0 \text{ mA}, V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$                       |

|                              |                   | V <sub>DD</sub> — 0.5 |        |                         | ٧    | $I_{OL} = -100 \mu\text{A}$                                                              |

| Output voltage, low          | V <sub>OL</sub>   |                       |        | 0.4                     | ٧    | $I_{OL} = 1.6 \text{ mA}, V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$                        |

|                              |                   |                       |        | 0.5                     | ٧    | $I_{OL} = 400 \mu\text{A}$                                                               |

| Input leakage current, high  | l <sub>LIH1</sub> |                       |        | 3                       | μΑ   | Except CL1, X1; V <sub>I</sub> = V <sub>DD</sub>                                         |

|                              | ILIH2             |                       | :      | 10                      | μΑ   | CL1, X1                                                                                  |

| Input leakage current, low   | I <sub>LIL1</sub> |                       |        | -3                      | μΑ   | Except CL1, X1; V <sub>I</sub> = 0 V                                                     |

|                              | I <sub>LIL2</sub> |                       |        | <b>−10</b>              | μA   | CL1, X1                                                                                  |

| Output leakage current, high | I <sub>LOH</sub>  |                       |        | 3                       | μΑ   | $V_0 = V_{DD}$                                                                           |

| Output leakage current, low  | I <sub>LOL</sub>  |                       |        | -3                      | μΑ   | $V_0 = 0 \text{ V}$                                                                      |

| Output impedance (1)         | R <sub>COM</sub>  | _                     | 3 -    | 5                       | kΩ   | COM <sub>0</sub> -COM <sub>3</sub> ; V <sub>DD</sub> = 4.5 to 6.0 V                      |

|                              |                   |                       | 5      | 15                      | kΩ   | COM <sub>0</sub> -COM <sub>3</sub>                                                       |

|                              | RS                |                       | 15     | 20                      | kΩ   | S <sub>0</sub> -S <sub>23</sub> ; V <sub>DD</sub> = 4.5 to 6.0 V                         |

|                              |                   |                       | 20     | 60                      | kΩ   | S <sub>0</sub> -S <sub>23</sub>                                                          |

| Supply voltage               | V <sub>DDDR</sub> | 2.0                   |        | 6.0                     | ٧    | Data retention mode                                                                      |

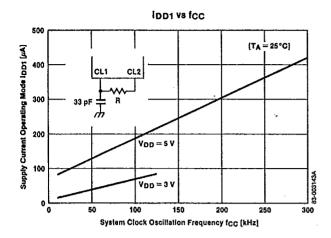

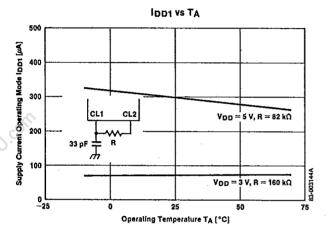

| Supply current               | l <sub>DD1</sub>  |                       | 300    | 900                     | μΑ   | Normal operation, $V_{DD}=5$ V $\pm$ 10%; R = 82 k $\Omega$ $\pm$ 2%, C = 33 pF $\pm$ 5% |

|                              |                   |                       | 70     | 300                     | μΑ   | Normal operation, $V_{DD}=3~V\pm10\%$ ; R = 160 k $\Omega$ ± 2%, C = 33 pF ± 5%          |

|                              | J <sub>002</sub>  |                       | 1.0    | 20                      | μΑ   | Stop mode, $X1 = 0 \text{ V}$ ; $V_{DD} = 5 \text{ V} \pm 10\%$                          |

| ·                            | •                 |                       | 0.3    | 10                      | μА   | Stop mode, $X1 = 0 \text{ V}$ ; $V_{DD} = 3 \text{ V} \pm 10\%$                          |

|                              | †DDDR             |                       | 0.2    | 10                      | μА   | Data retention mode, V <sub>DDDR</sub> = 2.0 V                                           |

<sup>(1)</sup>  $V_{LCD} = 2.7 \text{ V to } V_{DD}$   $V_{LCD1} = V_{DD} - (1/3) V_{LCD}$   $V_{LCD2} = V_{DD} - (2/3) V_{LCD}$   $V_{LCD3} = V_{DD} - V_{LCD}$

#### **AC Characteristics 1**

For  $V_{DD} = 2.7$  to 6.0 Volts  $T_A = -10$  to +70 °C

|                                    |                                       | Limits   |     |      |      | Test                                                                              |

|------------------------------------|---------------------------------------|----------|-----|------|------|-----------------------------------------------------------------------------------|

| Parameter                          | Symbol                                | Min      | Тур | Max  | Unit | Conditions                                                                        |

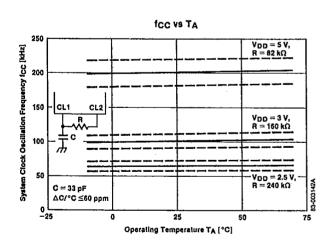

| System clock frequency             | fcc                                   | 150      | 200 | 240  | kHz  | $V_{DD} = 5 \text{ V} \pm 10\%; R = 82 \text{ k}\Omega \pm 2\% \text{ (Note 1)}$  |

|                                    |                                       | 75       | 100 | 120  | kHz  | $V_{DD} = 3 \text{ V} \pm 10\%; R = 160 \text{ k}\Omega \pm 2\% \text{ (Note 1)}$ |

|                                    |                                       | 75       |     | 135  | kHz  | R = 160 kΩ ±2% (Note 1)                                                           |

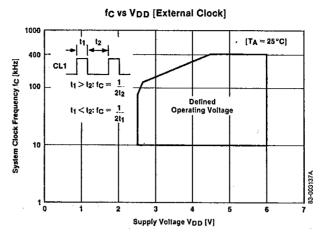

|                                    | f <sub>C</sub>                        | 10       |     | 410  | kHz  | CL1, external clock, 50% duty; $V_{DD} = 4.5 \text{ to}$ 6.0 V                    |

|                                    |                                       | 10       |     | 125  | kHz  | CL1, external clock, 50% duty; V <sub>DD</sub> = 2.7 V                            |

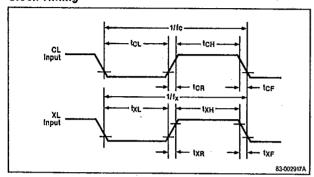

| System clock rise and fall<br>ime  | t <sub>CR</sub> , t <sub>CF</sub>     |          |     | 0.2  | μ\$  | CL1, external clock                                                               |

| System clock pulse width           | t <sub>CH</sub> , t <sub>CL</sub>     | 1.2      |     | 50   | μS   | CL1, external clock; V <sub>DD</sub> = 4.5 to 6.0 V                               |

|                                    |                                       | 4.0      |     | 50   | μS   | CL1, external clock; V <sub>DD</sub> = 2.7 V                                      |

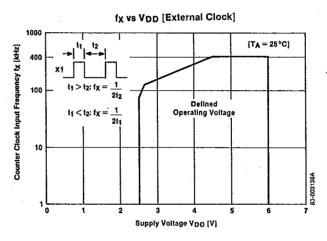

| Counter clock frequency            | fxx                                   | 25       | 32  | 50   | kHz  | X1, X2, crystal oscillator                                                        |

|                                    | fX                                    | 0        |     | 410  | kHz  | X1, external pulse input, 50% duty;<br>V <sub>DD</sub> = 4.5 to 6.0 V             |

|                                    |                                       | 0        |     | 125  | kHz  | X1, external pulse input, 50% duty;<br>V <sub>DD</sub> = 2.7 V                    |

| Counter clock rise and fall<br>ime | txn, txf                              |          |     | 0.2  | μS   | X1, external pulse input                                                          |

| Counter clock pulse width          | t <sub>XH</sub> , t <sub>XL</sub>     | 1.2      |     |      | μS   | X1, external pulse input; $V_{DD} = 4.5$ to 6.0 \                                 |

|                                    |                                       | 4.0      |     |      | μS   | X1, external pulse input; $V_{DD} = 2.7 \text{ V}$                                |

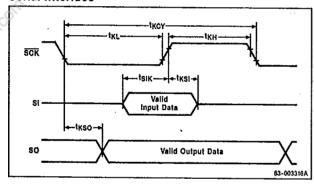

| CK cycle time                      | <sup>t</sup> KCY                      | 3.0      |     |      | μs   | SCK as input; V <sub>DD</sub> = 4.5 to 6.0 V                                      |

|                                    |                                       | 8.0      |     |      | μS   | SCK as input                                                                      |

|                                    |                                       | 4.9      |     |      | μs   | SCK as output; V <sub>DD</sub> = 4.5 to 6.0 V                                     |

|                                    |                                       | 16.0     |     |      | μs   | SCK as output                                                                     |

| BCK pulse width                    | t <sub>KH</sub> , t <sub>KL</sub>     | 1.3      |     |      | μ\$  | $\overline{\text{SCK}}$ as input; $V_{DD} = 4.5 \text{ to } 6.0 \text{ V}$        |

|                                    |                                       | 4.0      |     |      | μ\$  | SCK as input                                                                      |

|                                    |                                       | 2.2      |     |      | μS   | SCK as output; V <sub>DD</sub> = 4.5 to 6.0 V                                     |

|                                    |                                       | 8.0      |     |      | μS   | SCK as output                                                                     |

| SI setup time to SCK 1             | tsik                                  | 300      |     |      | ns   |                                                                                   |

| SI hold time after SCK 1           | t <sub>KSI</sub>                      | 450      |     |      | กร   |                                                                                   |

| 30 delay time after SCK ↓          | t <sub>KSO</sub> -                    |          |     | 850  | ns   | V <sub>DD</sub> = 4.5 V to 6.0 V                                                  |

|                                    |                                       |          |     | 1200 | ns   |                                                                                   |

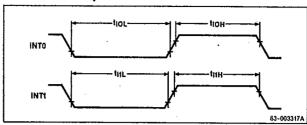

| NTO pulse width                    | t <sub>IOH</sub> , t <sub>IOL</sub>   | 10       |     |      | μS   |                                                                                   |

| NT1 pulse width                    | t <sub>1111</sub> , t <sub>111.</sub> | (Note 2) |     |      | μS   |                                                                                   |

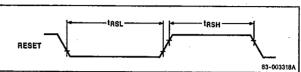

| RESET pulse width                  | trsh, trsl                            | 10       |     |      | μS   |                                                                                   |

| RESET setup time                   | tsas                                  | 0        |     |      | ns   |                                                                                   |

|                                    |                                       |          |     |      |      |                                                                                   |

#### Notes:

<sup>(1)</sup> RC network at CL1 and CL2; C = 33 pF  $\pm 5\%$ ,  $\Delta C/^{\circ}C \leq 60$  ppm.

<sup>(2)</sup>  $2 \times 10^3 \div f_{CC}$  or  $f_C$  in kHz.

For  $V_{DD} = 2.5$  to 3.3 Volts  $T_A = -10$  to +70 °C

|                                  |                                     | Limits   |     |             |             | Test                                                                       |

|----------------------------------|-------------------------------------|----------|-----|-------------|-------------|----------------------------------------------------------------------------|

| Parameter                        | Symbol                              | Min      | Тур | Max         | Unit        | Conditions                                                                 |

| System clock frequency           | fcc                                 | 50       |     | 80          | kHz         | R = 240 kΩ ±2% (Note 1)                                                    |

|                                  |                                     | 50       | 64  | 77          | kHz         | $V_{DD} = 2.5 \text{ V; R} = 240 \text{ k}\Omega \pm 2\% \text{ (Note 1)}$ |

|                                  | fc                                  | . 10     |     | 80          | kHz         | CL1, external clock, 50% duty                                              |

| System clock rise and fall time  | t <sub>CR</sub> , t <sub>CF</sub>   |          | -   | 0.2         | μ5          | CL1, external clock                                                        |

| System clock pulse width         | t <sub>CH</sub> , t <sub>CL</sub>   | 6.25     | -   | 50          | <i>μ</i> \$ | CL1, external clock                                                        |

| Counter clock frequency          | f <sub>XX</sub> .                   | 25       | 32  | 50          | kHz         | X1, X2, crystal oscillator                                                 |

|                                  | f <sub>X</sub>                      | 0        |     | 80          | kHz         | X1, external pulse input, 50% duty                                         |

| Counter clock rise and fall time | t <sub>XR</sub> , t <sub>XF</sub>   |          |     | 0.2         | μS          | X1, external pulse input                                                   |

| Counter clock pulse width        | t <sub>XH</sub> , t <sub>XL</sub>   | 6.25     |     |             | μS          | X1, external pulse input                                                   |

| SCK cycle time                   | tKCY                                | 12.5     |     |             | μs          | SCK as input                                                               |

|                                  |                                     | 25       |     | <del></del> | μS          | SCK as output                                                              |

| SCK pulse width                  | t <sub>KH</sub> , t <sub>KL</sub>   | 6.25     |     |             | μS          | SCK as input                                                               |

|                                  |                                     | 11.5     |     |             | μS          | SCK as output                                                              |

| SI setup time to SCK 1           | tsik                                | 1        |     |             | μS          |                                                                            |

| SI hold time after SCK †         | t <sub>KSI</sub>                    | 1        |     |             | μS          | -                                                                          |

| SO delay time after SCK ‡        | tkso                                |          |     | 2           | μS          |                                                                            |

| INTO pulse width                 | t <sub>IOH</sub> , t <sub>IOL</sub> | 30       |     |             | μS          |                                                                            |

| NT1 pulse width                  | <b>411Н. 411</b> L                  | (Note 2) |     |             | μS          |                                                                            |

| RESET pulse width                | t <sub>RSH</sub> , t <sub>RSL</sub> | 30       |     |             | μ\$         |                                                                            |

(1) RC network at CL1 and CL2;  $C = 33 \text{ pF} \pm 5\%$ ,  $\triangle C/^{\circ}C \le 60 \text{ ppm}$ .

(2)  $2 \times 10^3 \div f_{CO}$  or  $f_C$  in kHz.

#### **Recommended R and C Values for System Clock Oscillation Circuit**

$T_A = -10 \text{ to } +70 \,^{\circ}\text{C}$

| Supply Voltage Range | Recommended<br>Values (Note 1)     | Frequency Range                    |  |  |

|----------------------|------------------------------------|------------------------------------|--|--|

| 4.5 to 6.0 V         | $R=82 \text{ k}\Omega \pm 2\%$     | 150 to 250 kHz,<br>200 kHz typical |  |  |

| 2.7 to 3.3 V         | R =160 kΩ ±2%                      | 75 to 120 kHz,<br>100 kHz typical  |  |  |

| 2.7 to 6.0 V         | R =160 kΩ± 2%                      | 75 to 135 kHz                      |  |  |

| 2.5 to 3.3 V         | R = 240 kΩ ±2%                     | 50 to 80 kHz                       |  |  |

| 2.5 to 6.0 V         | $R = 240 \text{ k}\Omega \pm 2 \%$ | 50 to 85 kHz                       |  |  |

#### Note:

(1)  $C = 33 \text{ pF } \pm 5\%$ ,  $|\Delta C/^{\circ}C| \leq 60 \text{ ppm}$ .

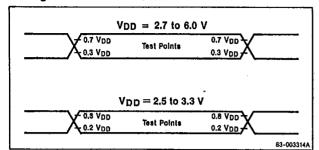

#### **Timing Waveforms**

#### **Timing Measurement Points**

#### External Interrupts

#### **Clock Timing**

#### Reset

#### **Data Retention Mode**

#### Serial Interface

#### **Operating Characteristics**

$T_A = 25$  °C

NEC

#### **Operating Characteristics (cont)**